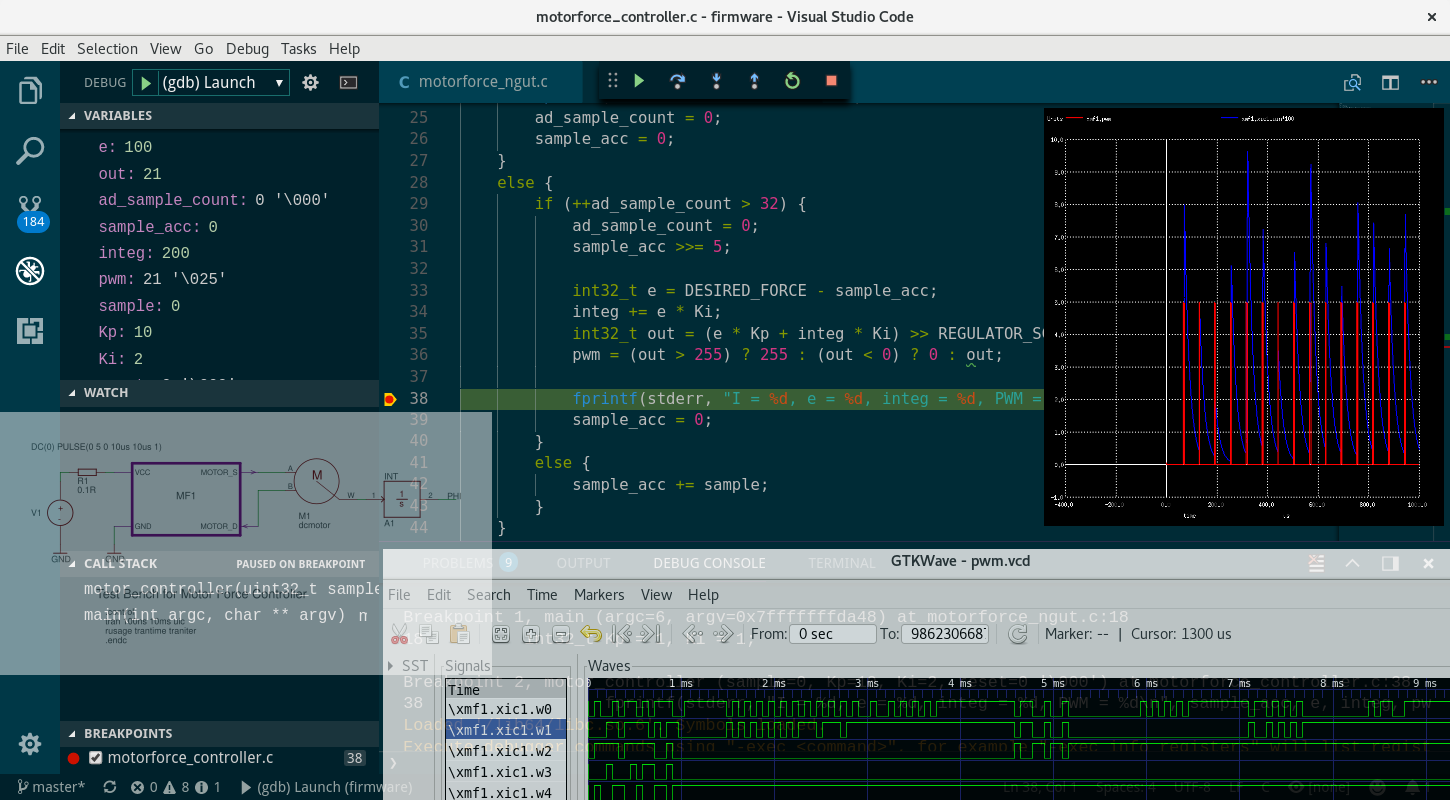

Mixed Signal & Domain Simulation for Embedded Worlds

Bringing Open-Source Tools Together¶

Key challenge was to find a working combinations of mature packages to get a usable and working solution of Verilog simulation with mixed-signal spice. Here is the list of open-source software that you will need to begin with mixed-signal and Verilog simulations:

ngSpice - Mixed Signal Simulation¶

Spice originally developed in Berkeley has gone many ways and it’s concepts and core can be found in numerous forks. Here we propose a very well packaged version of spice called ngspice featuring:

standard spice core based on spice 3f4

mixed signal xspice core

extension to verilog-A models

T-CAD spice simulation

tcl scripting

In addition Isotel NgSpice Fork on SourceForge adds

co-simulation of C/C++ or other languages

and in addition MixedSim Open-Source Library on GitHub provides:

all examples found in these articles

and Eagle supporting ULP and library.

Installation procedure for ngspice is described in user manual. The MixedSim Open-Source lib just needs to be downloaded, no extra installation steps are needed.

Yosys - Verilogy RTL synthesis¶

Yosys developed by Clifford Wolf is a framework for Verilog RTL synthesis with extensive Verilog-2005 support provides a basic set of synthesis algorithms for various application domains. Selected features and typical applications:

Process almost any synthesizable Verilog-2005 design

Converting Verilog to BLIF / EDIF/ BTOR / SMT-LIB / simple RTL Verilog / etc.

Built-in formal methods for checking properties and equivalence

Mapping to ASIC standard cell libraries (in Liberty File Format)

Mapping to Xilinx 7-Series and Lattice iCE40 FPGAs

Foundation and/or front-end for custom flows

Installation procedure is described in user manuals.

iverilog - Icarus Verilog¶

Icarus Verilog is a Verilog simulation and synthesis tool. It operates as a compiler, compiling source code written in Verilog (IEEE-1364) into some target format.

Written by Stephen Williams is one of the most popular free verilog simulators. It’s a part of every linux distribution, for details on installation see Installation Guide.

gtkwave - viewer¶

GTKWave is an analysis tool used to perform debugging on Verilog or VHDL simulation models. GTKWave has been developed to perform debug tasks on large systems on a chip and has been used in this capacity as an offline replacement for third-party debug tools. It features two interlocking tools:

gtkwave, is the waveform analyzer and is the primary tool used for visualization, and

rtlbrowse, is used to view and navigate through RTL source code.

It’s a part of every linux distribution. Installation instructions and user guide can be found on this link.

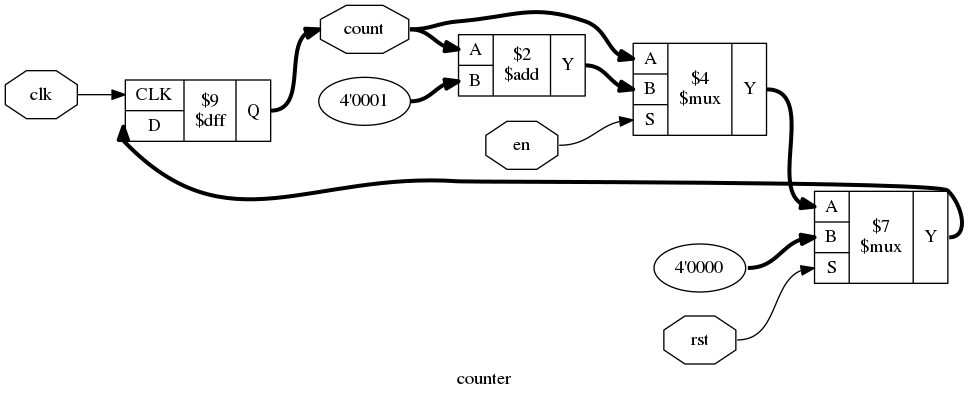

graphviz - Visualization tool¶

Graph visualization is a way of representing structural information as diagrams of abstract graphs and networks. It is needed to display synthesized verilog output from the Yosys.

It’s a part of every linux distribution, for other systems please follow the download page.

Continue to Mixed Signal Simulation Concept