Mixed Signal & Domain Simulation for Embedded Worlds

Mixed Signal Simulation Concept¶

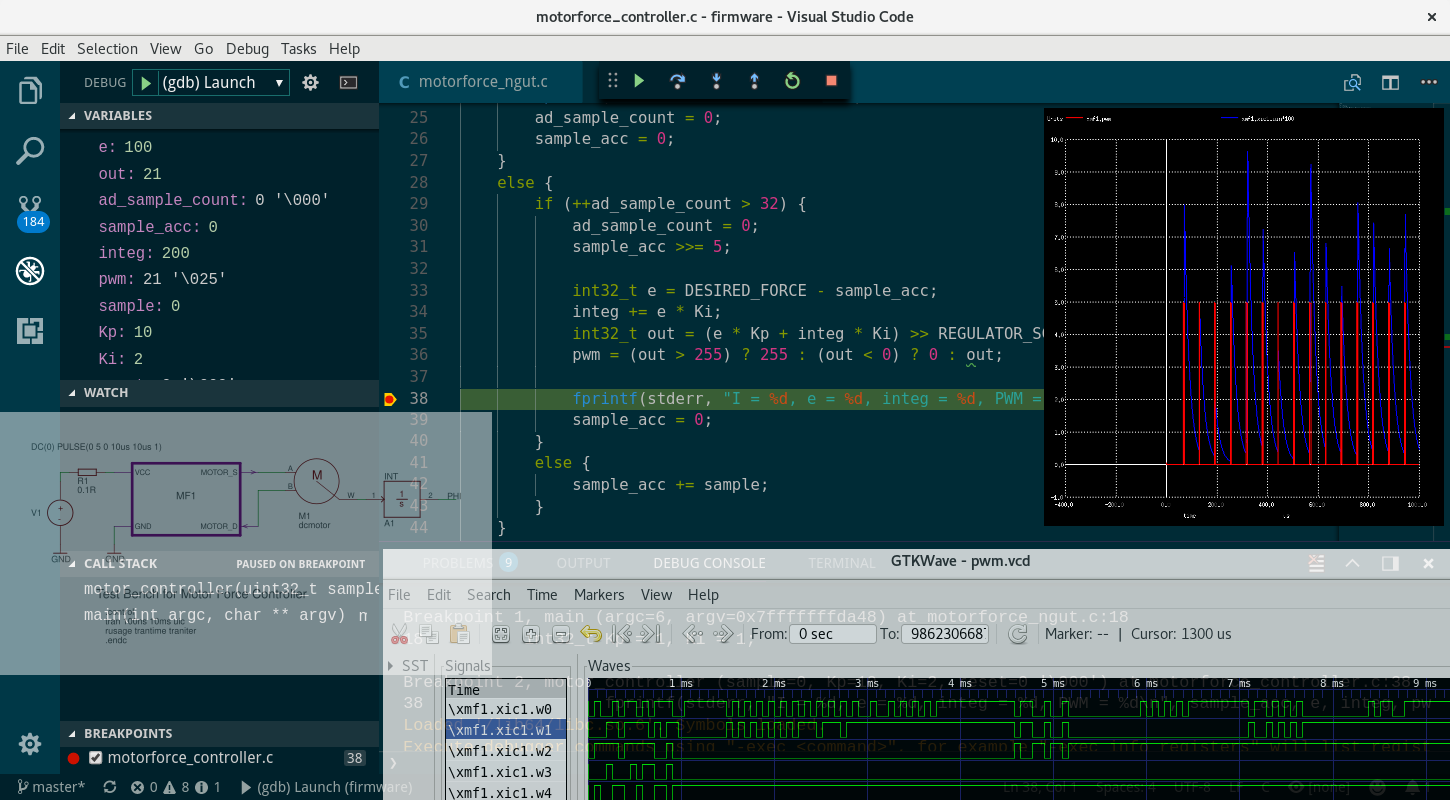

Process flow and dependencies are shown in the following diagram:

Organized as:

the upper horizontal line represents digital simulation,

the middle horizontal line digital synthesis, and

the bottom horizontal line mixed signal simulation.

Blocks in:

yellow represent user input, so at the top is the digital verilog entry, and below is the spice circuit entry,

green blocks represent yosys synthesis with technology libraries,

cyan block represent output from the yosys synthesis in spice sub-circuit format,

blocks without color represent stand-alone programs without cross related dependencies.

Verilog Simulation¶

Verilog development and simulation follows procedures as described under iverilog simulation guide. I recommend you to write a test bench for each independent module and test it well before continuing into a mixed signal simulation. Also note that pure digital simulation is still of several orders faster than mixed signal simulation.

Verilog Synthesis¶

Transforms verilog code into primitive elements such as simple gates NOT, NOR, NAND, XOR, and basic flip-flops as latch, and D-flip-flop. Verilog code to be synthesized should only use synthesizable elements as described in this lectures slides by Chihhao Chao, NTU.

Synthesis requires a technology library which defines the elements to which it must map the logic. For the same elements as used during synthesis by the yosys a technology library must be prepared for spice simulation.

Mixed Signal Simulation¶

The ngspice core consist of standard spice3f4 analog simulation and the xspice event-driven simulation with additional 12 digital node types: 0s, 1s, Us, 0r, 1r, Ur, 0z, 1z, Uz, 0u, 1u, Uu, see section 12.5.1 Digital Node Types on page 236/624 of ngspice user guide.

The ngspice netlist represents the top netlist used to combine verilog synthesized parts and analog parts together:

spice generated sub-circuits from yosys,

yosys technology library,

and our spice circuit with modules (sub-circuits).

In addition we need to add bridges that connect the analog and digital worlds together to map between the real numbers from analog part to 12 states of the digital node types. These are called hybrid models. Special care must be taken into undefined states, which map to some predefined values in analog space. ngspice in addition may import Verilog-A modules.